# microwave

## contents

VOLUME 25, NUMBER 11 USPS 396-250 **NOVEMBER 1982**

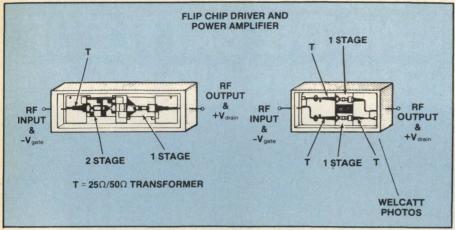

| BUSINESS/SPECIAL REPORTS GaAs MMICs — A Technology Assessment William R. Wisseman, Texas Instruments Incorporated                                                                                                             | 20              | Flip-Chip BeO Technology Applied<br>to GaAs Active Aperture Radars<br>P. Wallace, A. Wohlert and A.A. Immorlica, Jr.,<br>Microwave Semiconductor Corp. and D. Buck<br>Westinghouse Electric Corp.                 |                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

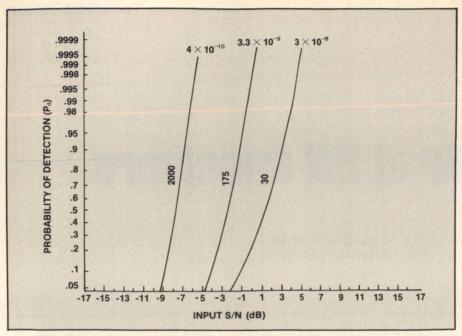

| 25th Anniversary Year Recollections                                                                                                                                                                                           | 55              | Sensitivity of EW Receivers                                                                                                                                                                                       | 115                                 |

| TECHNICAL/APPLICATIONS SECTION                                                                                                                                                                                                |                 | J.B.Y. Tsui and R. Shaw, Wright-Patterson AF                                                                                                                                                                      | В                                   |

| Microwave Switching With GaAs FETs<br>Yalcin Ayasli, Raytheon Research Division                                                                                                                                               | 61              | Source Power Leveling John Tarvin, EIP Microwave, Inc.                                                                                                                                                            | 123                                 |

| Yield Considerations In The Design<br>and Fabrication of GaAs MMICs<br>A.K. Gupta, W.C. Petersen and D.R. Decker,<br>Rockwell International Microelectronics<br>Research and Development Center                               | 77              | A New Method For Displaying Fields A.J. Baden Fuller, Department of Engineering, University of Leicester, Leicester, England, and Dr. M.L.X. dos Santos, Pontificia Universidade Catolica, Rio de Janeiro, Brazil | 128                                 |

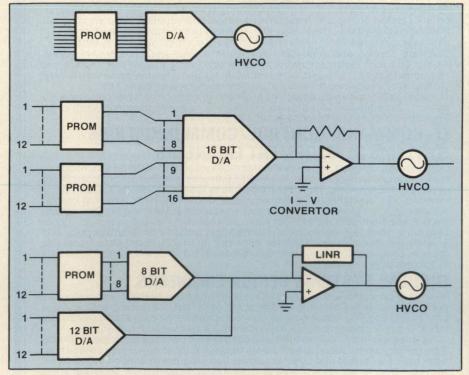

| Broadband Monolithic Integrated Power<br>Amplifier in Gallium Arsenide<br>M.C. Driver, G.W. Eldridge and J.E. Degenford,<br>Westinghouse R & D Center                                                                         | 87              | Digitally Tuned PROM-Corrected VCO Watkins-Johnson DEPARTMENTS                                                                                                                                                    | 131                                 |

| Hybrid vs Monolithic H. Yamasaki and D. Maki, Torrance Research Center, Hughes Aircraft Company                                                                                                                               | 95              | Coming Events International Marketplace Workshops and Courses Sum Up                                                                                                                                              | 17<br>17-1*<br>18<br>18             |

| Monolithic GaAs FET Low-Noise<br>Amplifiers For X-Band Applications<br>G.E. Brehm and R.E. Lehmann,<br>Texas Instruments Incorporated,<br>Central Research Laboratories                                                       | 103             | News from Washington International Report Around the Circuit Letters Product Feature Book Review                                                                                                                  | 39<br>45<br>50<br>136<br>138<br>140 |

| ON THE COVER: Fast-tuning VCOs with digital tuning and PROM correwill compete with YIG oscillators for wide band, linearity applications. Watkins-Johnson's entry in the is described in the Cover Story beginning on p. 131. | high<br>e field | Erratum Microwave Products Ad Index and Sales Reps. New Literature *Euro-Global Edition Only.                                                                                                                     | 141<br>142<br>153<br>154            |

#### STAFF

**Vice President/** General Manager Bernard B. Bossard

design by Owen Finstad, Art Director, Watkins-Johnson Co.

Publisher/Editor Howard I. Ellowitz Consulting Editors Theodore S. Saad Dr. Joseph F. White

Assistant Editor John S. Haystead Editorial Assistant Greg Porell Washington Editor Gerald Green **Production Manager** Craig Landay Assoc. Art Director Jane C. Reed Circulation Manager Robyn Thaw Advertising Manager F. Lee Murphy, Jr.

#### IN EUROPE

**Advertising Coordinator** Bronwyn Holmes Editorial Assistant Frances Grant

#### CORPORATE OFFICERS

President William Bazzy

Executive Vice President Richard J. Briden Group Vice President Bernard B. Bossard

#### SENIOR ASSOCIATE **EDITORS**

Dr. F. A. Brand Dr. S. B. Cohn Dr. R. C. Hansen Dr. B. Lax

#### ASSOCIATE **EDITORS**

H. Warren Cooper V. G. Gelnovatch Dr. J. Kuno

#### **EDITORIAL REVIEW BOARD**

Dr. F. Arams Dr. R. C. Baird D. K. Barton Dr. E. F. Belohoubek K. J. Button H. F. Chapell Dr. I. Drukier

M. Fahey Dr. F. E. Gardiol R. Garver Dr. A. Gilardini Dr. M. A. K. Hamid J. L. Heaton E. E. Hollis J. S. Hollis H. Howe Dr. P. A. Hudson A. Kelly R. Knowles Dr. L. Lewin S. March Dr. G. L. Matthaei W. G. Matthei M. A. Maury, Jr. Dr. D. N. McQuiddy Dr. R. L. Metivier C. K. S. Miller

W. W. Mumford

S. S. Oleesky

Dr. N. S. Nahman

Dr. J. D. Dyson

Dr. L. J. Ricardi Dr. L. Reibman Dr. G. F. Ross J. Rush Dr. J. A. Saloom H. Stinehelfer

Press run for this issue is 45,025 copies.

Dr. J. M. Osepchuk Dr. H. E. Stockman N. H. Pond J. J. Taub W. L. Pritchard R. Tenenholtz Dr. W. A. G. Voss M. D. Waldman Dr. B. O. Weinschel Dr. P. Weissglas Dr. J. Wiltse Dr. E. Wolff

#### EXECUTIVE EDITORIAL OFFICE

610 Washington Street, Dedham. MA 02026 Tel: 617 326-8220 710 348-0481 TELEX: 951-659 MICROSOL DEDM

#### EUROPEAN EDITORIAL OFFICE

25 Victoria Street London SW1H OEH England Tel: 01-222-0466 **TELEX:** 885744

Microwave Journal is issued without charge upon written request to qualified persons working in that portion of the electronics industry including governmental and university installation that deal with VHF through light frequencies. Other subscriptions; domestic, \$36 per year, two year subscriptions \$65; foreign, \$48 per year, two year subscriptions \$85: back issues (if available) and single copies \$5.00.

Copyright® 1982 by Horizon House-Microwave, Inc. Microfilm copies of Microwave Journal 300 N. Zeeb Rd., Ann Arbor, MI 48106 are available from University Microfilms.

POSTMASTER: send address corrections to Microwave Journal, 610 Washington Street, Dedham MA 02026.

Horizon House also publishes Telecommunications and Journal of Electronic Defense

# Microwave Switching With GaAs FETs

### **Device and Circuit Design Theory and Applications**

Yalcin Ayasli Raytheon Research Division Lexington, MA

#### Introduction

There is a growing need for high-performance, small, versatile, and inexpensive microwave switches in phased-array systems and electronic warfare applications. The use of GaAs FETs as switch elements to help meet these needs has been reported recently in various microwave applications<sup>1-7</sup>. These switches have already been demonstrated to provide subnanosecond switching speeds, multiwatt power-handling capability, virtually zero control power dissipation, and compatibility with monolithic applications.

This article discusses the design considerations for a switch FET.

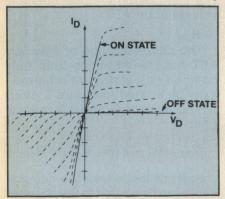

Fig. 1 Two linear operation regions of an FET switch.

theoretical determination of its equivalent circuit under switching conditions, rf and dc circuit design requirements, and large-signal operation considerations for power switching applications. Design examples and experimental data from monolithic TR switches, phase shifters, and high-power switches will be given.

#### GaAs FET as a Switch

The FET switch is a three-terminal device with the gate voltage  $V_{\rm g}$  controlling the switch states. In a

typical switch mode, the high impedance state corresponds to a negative gate bias larger in magnitude than the pinchoff voltage ( $|V_g| > |V_p|$ ), and the low impedance state corresponds to zero gate bias. These two linear operation regions of the FET are shown schematically in Figure 1.

Note that in either state virtually no dc bias power is required. Therefore the switches can practically be classified as passive as far as the overall power consumption is concerned: this leads to enor-

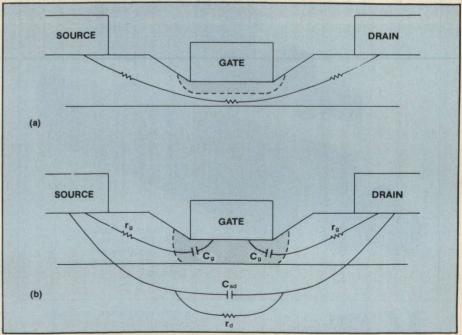

Fig. 2 Schematic cross-section of an FET showing various resistive and capacitive regions. a) No gate bias b)  $|V_g| > |V_p|$ .

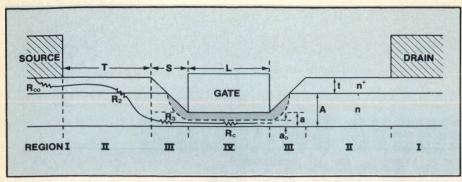

Fig. 3 Schematic cross-section of an FET showing various resistive sections contributing to the RoN of the switch.

AYDIN MICROWAVE TELECOMMUNICATIONS FOR THE 80'S

# Small in size... Big in Performance.

For more information, call or write: Aydin Microwave Division Marketing Department 75 East Trimble Rd., San Jose, Ca 95131 (408) 946-5600 TWX 910-338-0216 mous simplifications in driver requirements. Although the FET itself is a three-terminal device, the switch is bidirectional.

The cross-section of a simple FET structure appears in Figure 2. When no gate bias is applied, the channel is open except for the zero field depletion layer thickness. Hence, for current levels less than the saturated channel current ldss, the FET can be modeled as a linear resistor.

When a negative gate voltage  $V_g$  is applied between gate and source so that  $|V_g| > |V_{pinchoff}|$ , the channel can be completely depleted of free charge carriers. Under this bias condition, the FET can be modeled by series and parallel combination of resistors and capacitors. The approximate region of the FET responsible for each element is shown in Figure 2b.

Assuming that the gate termination represents a high rf impedance at the frequency of operation, the OFF-state equivalent circuit can be expressed as a parallel combination of a resistor and a capacitor. For  $1/\omega C_g >> r_g$ , the effective drain-to-source capacitor is simply  $(C_{sd} + C_g/2)$  and the effective drain resistor is the parallel combination of  $R_d$  and  $2/(\omega^2 C_g^2 r_g)$ . The figure of merit for a switch FET can simply be expressed as the ratio of its effective OFF state resistance to its ON resistance.

### Design Consideration for a Switch FET

Let us examine the effect of various device parameters on the device equivalent circuit. The important parameters are the channel geometry, gate length, the channel doping and the pinchoff voltage of the FET.

#### - RON

The ON resistance of a switch FET has contributions from four components, which are schematically illustrated in Figure 3. With the notation of Figure 3, it is clear that:

$$R_{ON} = R_c + 2 (R_{co} + R_2 + R_3).$$

Each of these resistive components can be related to the channel parameters of the FET. Let us examine each one separately.

R<sub>co</sub>: The constant resistance R<sub>co</sub> can be calculated as<sup>8</sup>:

$$R_{co} = \frac{2.1}{W t \, n_{+}^{0.66}} \, \Omega$$

where W is the gate periphery in mm, t the thickness of the  $n_+$  region under the source contact in  $\mu$ m.  $n_+$  is the doping density of the contact layer expressed in units of  $10^{16}$  cm<sup>-3</sup>.

R<sub>2</sub>: To estimate the value of R<sub>2</sub>, region II can be modeled in terms of incremental resistances, as shown in Figure 4.

Fig. 4 Equivalent incremental resistance circuit for calculating the contribution of Region II. a) actual resistance distribution b) approximate resistance distribution for R<sub>s</sub> >> r.

However, to obtain a simple formula, we can use the circuit model in Figure 4 when R<sub>s</sub> >> r. Making an analysis similar to Berger<sup>9</sup>, and using Fukui's formula for the resistivity of GaAs<sup>8</sup>, the resistance R<sub>2</sub> can be expressed in a closed-form equation as:

$$R_1 = \frac{1.1 \text{ T}}{\text{W t n}_+^{.82}} + \frac{1.1}{\text{w n}^{.82}} \left( \frac{\text{A-a}}{\text{a}} \right)^{0.5} \Omega .$$

In this paper, all the doping levels are in units of 10<sup>16</sup> cm<sup>-3</sup>, and all the lengths are expressed in  $\mu$ m except the gate periphery W, which is in mm.

R<sub>3</sub>: This is the contribution of the bevelled section. Here it is difficult to define the current paths with any accuracy. We will assume that the conduction region is confined

#### TABLE I

### CALCULATION OF EQUIVALENT CIRCUIT PARAMETERS FOR A TYPICAL 1 MM GaAs FET SWITCH

#### **Design Parameters**

W = 1 mm

L = 1

$$\mu$$

$V_p = -4 V$

$n = 10^{17} \text{ cm}^{-3}$

$n^+ = 2 \times 10^{18} \text{ cm}^{-3}$

$A = .37 \mu \text{m}$

$T = 2 \mu \text{m}$

$S = 0.3 \mu \text{m}$

$t = 0.2 \mu \text{m}$

$a_0 = 0.15 \mu \text{m}$

$a = 0.26 \mu \text{m}$

#### **Equivalent Circuit Parameters**

$\begin{aligned} R_{\text{ON}} &= 2.7 \, \Omega \\ C_{\text{sd}} &= 0.14 \; \text{pF} \\ R_{\text{OFF}} &= 3 \; \text{K} \; \Omega \\ R_{\text{g}} &= 1.4 \, \Omega \\ C_{\text{g}} &= 0.22 \; \text{pF} \end{aligned}$

to a region of height a and length S. If we further assume that the slope of the bevel is  $45^{\circ}$ , then S = t + A-a. Hence,  $R_3$  becomes:

$$R_3 = \frac{1.1 (t + A - a)}{W a n^{.82}} \Omega$$

.

R<sub>c</sub>: The open channel resistance can be estimated as<sup>8</sup>:

$$R_c = \frac{1.1 L}{W a_0 n^{.82}} \Omega .$$

In this equation,  $a_o$  is the fraction of the channel which is open. For GaAs FETs with a given pinchoff voltage  $V_p$  and channel doping, it can be calculated as:

$$a_0 = \frac{.378}{n^{0.5}} (V_p + 0.85)^{0.5} - (0.85)^{0.5}$$

The channel resistance calculated through the equations above is typically a lower limit to what one observes experimentally. This could be due to the proximity of the interface between the channel and buffer layer, which makes it difficult to precisely define either the mobility or the doping level under the gate.

#### OFF-State Equivalent Circuit Parameters

C<sub>sd</sub>: The source-drain capacitance C<sub>sd</sub> represents the fringing capacitance between the source and drain electrodes.

A good estimate of these capacitances can be obtained by considering the electrostatic coupling between two parallel conductors on a surface of a semi-infinite dielectric medium, representing the GaAs chip. Using this model, the capacitance expression becomes <sup>10</sup>:

$$C_{sd} = (\varepsilon_r + 1) \varepsilon_o W \frac{K (1-k^2)^{1/2}}{K (k)}$$

where K (k) is the complete elliptic integral of the first kind. The argument k is related to the geometry of electrodes as:

$$k = \frac{(2L_s + L_{sd}) L_{sd}}{(L_s + L_{sd})^2}$$

<sup>1/2</sup>

where  $L_{sd}$  is the interelectrode spacing between the drain and source electrodes. In these expressions, it is assumed that  $L_s = L_d$  and  $L_s >> L_{sd}$ .

Source-drain capacitance is typically in the 0.14 pF range for 1 mm FETs and it is independent of device parameters such as channel doping and pinchoff voltage.

$r_d$ : The resistor in parallel with  $C_{sd}$  represents the rf losses associated with  $C_{sd}$ . Our experience indicates that 3 K  $\Omega$  for 1 mm gate devices representing a Q of around 25 at X-band frequencies is a reasonable choice.

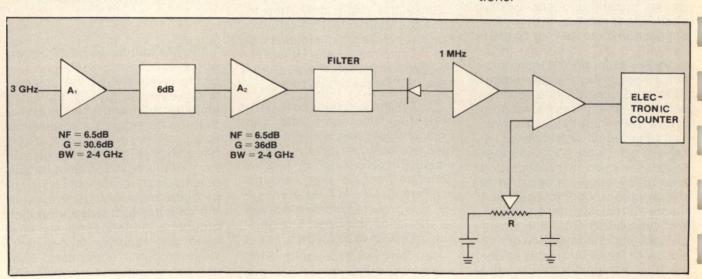

C<sub>g</sub>: C<sub>g</sub> represents the drain-togate and gate-to-source capacitances. These capacitances are equal because of symmetry. If there is a gate pad of significant area, its capacitance to ground needs to be added to the equivalent circuit.

There is no precise way of estimating C<sub>g</sub>. A simple-minded approach that gives C<sub>g</sub> values in good agreement with experimental results is to use half the gate capacitance with the channel fully depleted so that:

$$C_g = 0.06 \frac{WL}{a} pF$$

.

Note that a is related to both channel doping and the pinchoff voltage of the device.

[Continued on page 64]

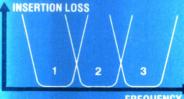

# directional couplers

19.5 dB

# 0.1 to 2000 MHz only \$79<sup>95</sup>(1-4)

AVAILABLE IN STOCK FOR IMMEDIATE DELIVERY

- rugged 11/4 in. sq. case

- 4 connector choices BNC, TNC, SMA and Type N

- connector intermixing male BNC, and Type N available

- low insertion loss, 1.5 dB

- flat coupling, ±1.0 dB

#### ZFDC 20-5 SPECIFICATIONS

| FREQUENCY (MHz) 0.1-2000<br>COUPLING, db 19.5 |        |      |

|-----------------------------------------------|--------|------|

| INSERTION LOSS, dB                            | TYP.   | MAX. |

| one octave band edge                          | 0.8    | 1.4  |

| total range                                   | 1.5    | 2.3  |

| DIRECTIVITY dB                                | TYP.   | MIN. |

| low range                                     | 30     | 20   |

| mid range                                     | 27     | 20   |

| upper range                                   | 22     | 10   |

| IMPEDANCE                                     | 50 ohr | ns   |

|                                               |        |      |

For complete specifications and performance curves refer to the 1980-1981 Microwaves Product Data Directory, the Goldbook or EEM

For Mini Circuits sales and distributors listing see page 85.

finding new ways . . . setting higher standards

### Mini-Circuits

A Division of Scientific Components Corporation

World's largest manufacturer of Double Balanced Mixers

2625 E. 14th St. B'klyn, N.Y. 11235 (212) 769-0200

C 87-3 REV. ORIG

r<sub>g</sub>: The resistor r<sub>g</sub> represents the changing resistance of C<sub>g</sub>. Again, we do not know a precise way of calculating this resistance. Experimental evidence suggests that one-half of R<sub>ON</sub> is a reasonable value for r<sub>g</sub>.

In the light of the discussion above, we can estimate the equivalent circuit of a typical GaAs switch FET. Table 1 summarizes typical channel parameters for a 1 mm total gate periphery, 1  $\mu$ m gate length FET with -4 V pinchoff voltage and 10<sup>17</sup> cm<sup>-3</sup> channel doping.

These equivalent circuit values translate to equivalent off-to-on resistance ratios of 800 at 10 GHz. This ratio decreases to 420 at 20 GHz, which is probably the end of the useful range for 1  $\mu$ m gate length switch FETs. To push the operating frequency to higher frequencies, one needs to go to submicron gate lengths to decrease  $C_g$  and  $R_{ON}$  and thus increase the switching equivalent resistance ratio.

We can also estimate the switching speed from the equivalent circuit. Assuming that the gate bias circuit is fed at 50 ohms impedance level and a total of 6 pFs are used in the bias circuit low pass filter, one reaches the conclusion that charging time constants are in the 0.3 nsec range. Experimental evidence also indicates that switching times of 1 nsec are quite possible, as shown in Figure 5. By optimizing the gate bias circuit design, switching times which are significantly smaller than 1 nsec are feasible.

#### **Circuit Design Considerations**

Switching circuits with FETs can be designed in essentially the same way as PIN diodes; this is done using on and off state equivalent circuits as required in the overall circuit configuration.

Although in this article we will discuss the monolithic circuit applications of switching FETs, it should be pointed out that it is quite possible also to use discrete FETs in hybrid form. Similar to PIN diodes, the FETs can be in series or shunt mode with respect to the transmission lines. There are, however, some salient features of FET

switch circuit design that need to be mentioned.

The FET is a three-terminal device; the switching occurs only through the gate control voltages and no other bias is required for the operation of the phase shifter. The rf transmission lines do not carry any dc voltage and therefore there is no need for dc blocking capacitors between various switch elements: a significant design advantage.

Gate control voltages corresponding to the two switch states are  $V_{g1} = OV$  and  $V_{g2} = -V$  where  $V > V_p$ . In either state, the gate junction is reverse biased and the gate current is either zero or negligible. Hence, the fact that switching control voltages need to be applied at negligible currents simplifies the requirements of the control circuit design.

In the off-state of the FET switch. note that gate-drain and gatesource capacitances are equal because both source and drain terminals are at ground potential. As a consequence of this, the drain terminal is not isolated from the gate terminal: the rf impedance of the gate bias circuit very much affects the equivalent drain-source impedance. In our designs, the gate bias circuit is configured as a two-section low pass filter providing an effective rf open to the FET at the gate terminal. When gate terminating impedance is very high, the equivalent drain-source capacitance can simply be approximated as C<sub>d</sub> + C<sub>o</sub>/2.

Note that the total drain capacitance shunting  $r_d$  represents a reactance of the order of 50 ohms at X-band frequencies. Therefore, to realize the switching action, this capacitance must be either resonated or its effect must be included in the design of the impedance matching sections. This is an important design consideration for FET switches, as it directly relates to the operation bandwidth.

Tuning out the effective drainsource capacitance can simply be accomplished by connecting an inductive reactance between the drain and source terminals. Monolithic circuit technology also allows distributing the switch FET and its associated drain capacitance along

[Continued on page 66]

# **frequency doublers**

+1 to +15 dBm input

## 1 to 1000 MHz only \$21<sup>95</sup> (5-24)

AVAILABLE IN STOCK FOR IMMEDIATE DELIVERY

- micro-miniature, 0.5 x 0.23 in. pc board area

- flat pack or plug-in mounting

- high rejection of odd order harmonics, 40 dB

- low conversion loss, 13 dB

- hermetically sealed

- ruggedly constructed MIL-M-28837 performance\*

\*Units are not QPL listed

#### SK-2 SPECIFICATIONS

| FREQUENCY RANGE, (MHz) INPUT 1-500 OUTPUT 2-1000   |                    |                    |

|----------------------------------------------------|--------------------|--------------------|

| CONVERSION LOSS, dB                                | TYP.               | MAX.               |

| 1-100 MHZ                                          | 13                 | 15                 |

| 100-300 MHz                                        | 13.5               | 15.5               |

| 300-500 MHz                                        | 14.0               | 16.5               |

| Spurious Harmonic Output, dB<br>2-200 MHz F1<br>F3 | TYP.<br>-40<br>-50 | MIN.<br>-30<br>-40 |

| 200-600 MHz F1<br>F3                               | -25<br>-40         | -20<br>-30         |

| 600-1000 MHz F1<br>F3                              | -20<br>-30         | -15<br>-25         |

For complete specifications and performance curves refer to the 1980-1981 Microwaves Product Data Directory, the Goldbook or EEM.

For Mini Circuits sales and distributors listing see page 85.

finding new ways . . . setting higher standards

## Mini-Circuits

A Division of Scientific Components Corporation World's largest manufacturer of Double Balanced Mixers 2625 E. 14th St. B'klyn, N.Y. 11235 (212) 769-0200

[From page 64] MICROWAVE SWITCHING

RF FREQUENCY 10 GHZ

RF OUTPUT 0 DBM

HORIZONTAL 1 NANOSECOND/DIVISION

HORIZONTAL

500 PICOSECONDS/DIVISION

SWITCH CONTROL SIGNAL HORIZONTAL: 2 ns/DIV VERTICAL: 1 V/DIV

Fig. 5 Monolithic TR switch switching data.

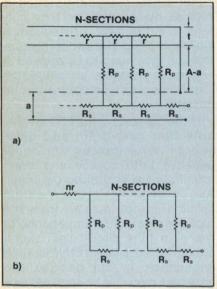

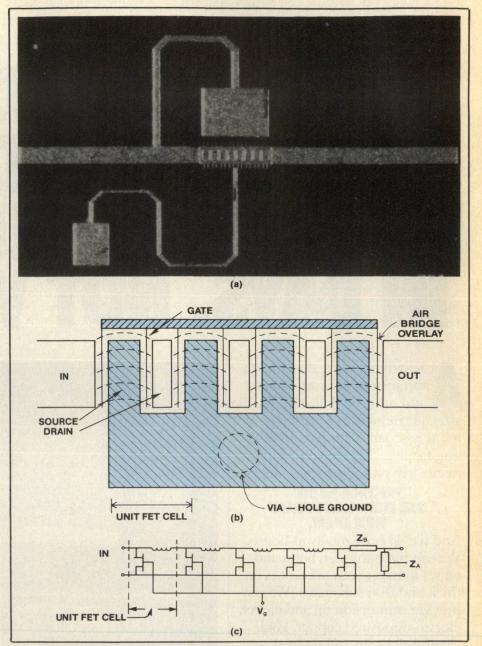

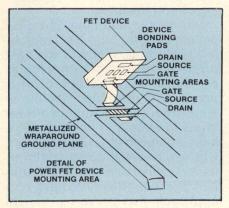

a transmission line structure. Consider the distributed switch approach shown in Figure 6<sup>5</sup>. In this structure, the drain-source capacitance and the overlay inductance are treated as the perunit-length capacitance and perunit-length inductance of an artificial transmission line. The source pad is grounded by a via hole.

The configuration shown in Figure 6 has two major design advantages: First, by integrating the FET into the rf transmission line, the intrinsic switch element of the FET is placed at the point where it is most effective. This eliminates the contribution of undesirable FET parasitic elements such as the drain pad capacitance and the extra transmission line sections that would have been required to connect a discrete FET to the rf line. Second, by including

the effect of the overlay inductance itself or by adding extra inductive elements between sections, the drain-source capacitance of the FET in the high impedance state can be effectively tuned out over a wider frequency range. When wide frequency band operation of FET switches is required, the distributed switch FET approach provides the solution.

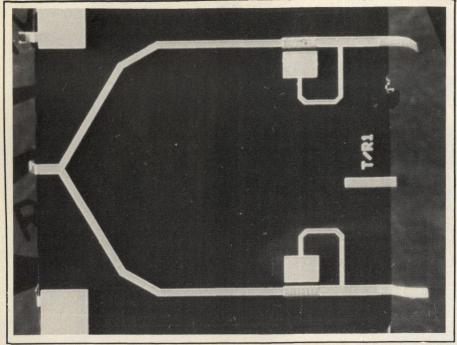

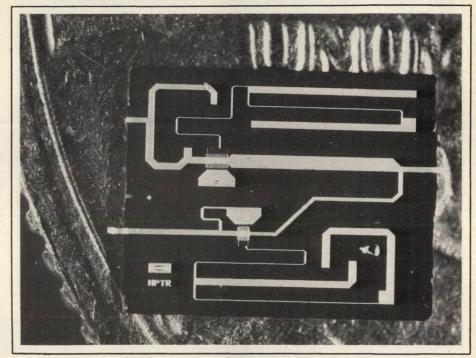

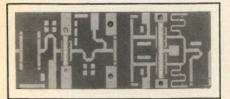

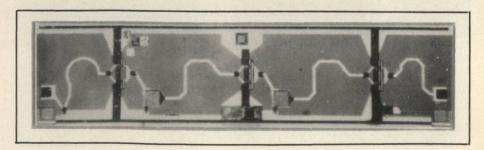

Figure 7 shows the chip picture of an X-band monolithic transmit/ receive switch3. The FETs have an interdigital structure with sixteen 100 µm wide channels. If two single-gate cells sharing a single drain finger are considered to be a unit cell, then there are eight unit cells connected by an overlay structure to form a lumped element transmission line. Because in this circuit the overlay inductance is small, it compensates only a fraction of the drain capacitance. The U-shaped shorted stub acts as the main tuning element. The experimental results for the switch indicate a 1 dB insertion loss bandwidth of 8-12 GHz with minimum insertion loss around 0.5 dB. Isolation between the transmit and receive arms is better than 30 dB across the band. The chip dimensions are 3 x 3 x 0.1 mm.

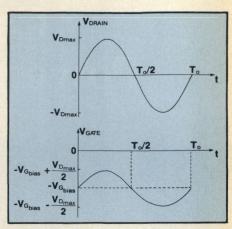

For microwave power switching using FETs, there are additional considerations. One of these considerations is the maximum allowable rf voltage swing across the device. The variation of the rf voltage on the drain and gate terminals with respect to the grounded source is shown in Figure 8 for one period<sup>7</sup>.

In this figure, it is assumed that the gate terminal of the switch FET is rf open. This condition should be realized in the design of the gate bias circuitry.

Under the above assumption and because gate-to-drain impedance and gate-to-source impedance are equal, half of the drain voltage swing appears in the gate terminal, as illustrated in Figure 8. Constraints on the terminal voltages can be summarized as follows. During the first half of the period, the total gate voltage should not fall below the pinchoff voltage V<sub>p</sub>. During the entire cycle, the difference between the drain and gate

[Continued on page 68]

## MICROWAVE MILLIMETERS

Microwave tuning elements offer a convenient and economical method for tuning cavities, waveguides and other microwave structures. The unique Johanson self-locking constant torque drive mechanism eliminates the need for locking nuts and assures stable noise free adjustment in applications from L to W band. Available in a variety of applications in metallic, dielectric and resistive materials.

Electronic Accuracy Through Mechanical Precision

Manufacturing Corporation

400 Rockaway Valley Road Boonton, New Jersey 07005 201-334-2676 TWX 710-987-8367

Fig. 6 Monolithic distributed switch approach. a) 1 × 1 switch in monolithic form b) FET structure c) equivalent circuit.

voltages should not exceed the gate-drain breakdown voltage. These contraints can be expressed mathematically as:

$$-V_{G_{bias}} + \frac{V_{Dmax}}{2} = -V_{p}$$

$$V_{Dmax} + V_{G_{bias}} = \frac{V_{Dmax}}{2} = V_B .$$

From these two equations, the maximum allowable drain voltage and the required gate bias condition can be solved as:

$$V_{Dmax} = V_B - V_p$$

and

$$V_{G_{bias}} = \frac{V_B + V_p}{2}$$

.

Hence, if the impedance level that the switch FET sees in its high impedance state is Zo, then the maximum power that can be transmitted in the switch closed position can be calculated as:

$$P_{\text{max}} = \frac{1}{2} \frac{(V_B - V_p)^2}{Z_0}$$

.

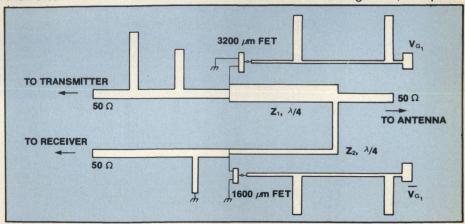

Using the notation of the schematic TR switch shown in Figure 9, Z<sub>o</sub> can approximately be calculated by transferring the 50 ohm antenna terminal impedance through the [Continued on page 70]

Fig. 7 X-band monolithic transmit/receive switch.

quarter wavelength MS line of characteristic impedance Z<sub>1</sub>, as:

$$Z_o \simeq \, \frac{Z_1^2}{50} \ .$$

Hence,

$$P_{\text{max}} = 25 \frac{(V_B - V_p)^2}{Z_1^2}$$

.

The maximum power calculation under switch closed condition is relevant to the transmitter arm of a transmit/receive (TR) switch. For the receiver arm, the constraints are different. During the time when the transmitter power is on, the

Fig. 8 Variation of the large signal rf voltages on drain and gate terminals over one period.

switch on the receiver arm is in the open state. In this low impedance condition, it should be able to sustain essentially the short circuited current in the receive arm due to the transmitter pulse. Again using the notation of Figure 9, the peak

Fig. 9 The schematic circuit diagram of the 10 W transmit-receive switch.

# MICROWAVE COMPONENT DELIVERY IS LIKE THE OLD SHELL GAME...

value of this current can be calculated as:

$$I_{\text{max}} = 20 \sqrt{\frac{P_{\text{Transmitted}_{\text{max}}}}{Z_2 (50 + Z_2)}}$$

switch open

Equations for Pmax and Imax fully specify the constraints on the switch FETs under power-switching conditions. First note that constraints on the transmitter and the receiver arm switches are completely independent. Also note that in the equation for P<sub>max</sub>, periphery of the device is not a parameter. Thus, once Z<sub>1</sub> is chosen from power requirements, the device periphery on the transmitter arm can be determined purely from small signal insertion loss analysis. On the other hand, the equation for Imax does bring in the device periphery as a design parameter for the receiver arm switch, since the maximum current that a device can support in its linear region before it reaches the saturation is directly proportional to its gate periphery. The characteristic impedance of the receiver arm, Z<sub>2</sub>, also enters into the equation. It is easy to see that, by increasing Z2, one can meet the requirement for Imax readily.

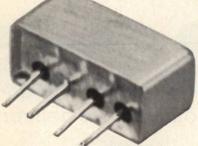

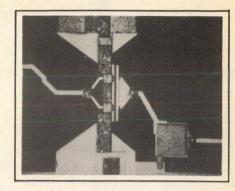

The switch described in Figure 9 is fabricated on 0.1 mm GaAs substrate<sup>7</sup>. A photograph of the finished chip is shown in Figure 10. The chip dimensions are 4.5 x 3.7 mm. In the transmit arm, a single-

gate, interdigitated 3.2 mm total gate periphery FET is used. The receive arm uses a single-gate FET of 1.6 mm total periphery.

The dc gate circuitry is provided monolithically on-chip. It is essentially a low pass filter which provides high impedance to the gate of the device and isolates the bias pad at the edge of the chip from rf leakage, at X-band frequencies.

The experimental data indicates insertion losses in the 0.8-1.6 dB range with higher than 25 dB isolation. No degradation from small

signal performance is observed up to 10 W of CW microwave power<sup>7</sup>.

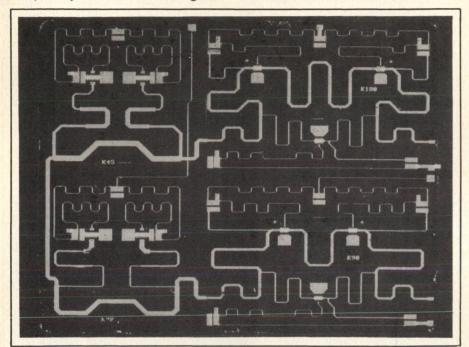

The FET switches, with their fast switching times and negligible dc power consumption, are ideal for passive phase-shifting circuits. As an example for this application, consider the X-band four-bit phase shifter chip shown in Figure 11 with 22.5°, 45°, 90° and 180° phase bits<sup>6</sup>. Starting in the upper right with the 180° bit, the microwave signal travels counterclockwise through the 45° (upper left), 22.5° (lower left) and 90° (lower right)

Fig. 10 Finished 10 W TR switch chip.

## SOMETIMES YOU COME UP A WINNER

(516) 543-4771

bits, exiting on the right edge of the chip. The circuit is passive and reciprocal so that the signal can equally well traverse this path in the opposite direction. The chip size is 6.4 x 7.9 x 0.1 mm.

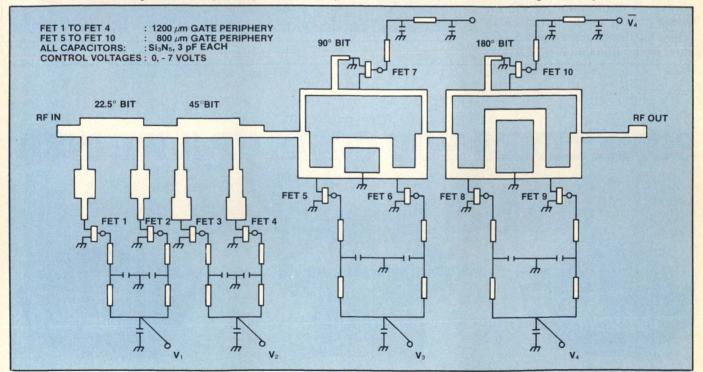

The schematic circuit diagram of the four-bit phase shifter is shown in Figure 12. The 22.5 and 45 degree bits are designed to provide constant phase shifts over the frequency bandwidth using the

loaded line technique. Each loading stub is composed of a suitably designed three section transforming and matching network which is terminated by a 1200  $\mu$ m switch FET. The principle of operation of this circuit and of the ones using PIN diodes is the same.

The 90° and 180° bits are designed using the switched-line technique. Note, however, that instead of the conventional four

switching elements, only three 800  $\mu$ m switch FETs are used in these circuits. Equal insertion loss between two phase states is maintained by designing the short and long arms of the phase shifter at different impedance levels.

For all bits, the switching is performed only through the gate control voltages and no other bias is required for the operation of the phase shifter. Thus, rf microstrip lines do not carry any dc voltage (in fact, they are dc grounded) and therefore there is no need for dc blocking capacitors between individual phase bit circuits.

Experimental performance of the phase shifter indicates 5.1 ± 0.6 dB insertion loss with 16 distinct phase states between 0° and 360°. The performance of the phse shifter is satisfactory for typical phase array applications. Their small size, negligible dc power requirements and subnanosecond switching times make the monolithic phase shifters good candidates for future frequency-agile airborne phasedarray systems.

#### Conclusions

The GaAs FET is examined in detail as a microwave frequency switching element. Its equivalent circuit as a switch is related to device geometry and channel

Fig. 11 Four-bit passive phase shifter chip.

Fig. 12 The schematic circuit diagram of the four-bit phase shifter.

[From page 72] MICROWAVE SWITCHING parameters. The rf circuit design considerations characteristic of FET switching circuits are discussed with examples from recent monolithic circuit designs. These examples demonstrate the versatility of GaAs FETs as switches.

When circuit size, dc power consumption, switching speed and producibility in large quantities are of prime importance, GaAs monolithic FET switch circuits will lead the way for future systems applications.

#### REFERENCES

- Gaspari, R.A., and H.H. Yee, "Microwave GaAs FET Switching," 1978 IEEE Inter-national Microwave Symposium Digest, pp. 58-60.

- 2. McLevige, W.V., and V. Sokolov, "Microwave Switching with Parallel-Resonated GaAs FETs," IEEE Electron Device Lett. (8), (Aug. 1980).

- 3. Ayasli, Y., R.A. Pucel, J.L. Vorhaus, and W. Fabian, "A Monolithic X-Band Single-Pole, Double-Throw Bidirectional GaAs FET Switch," IEEE GaAs Integrated Circuits Symposium, Nov. 4-6, 1980.

- 4. McLevige, W.V., and V. Sokolov, "Reso-nated GaAs FET Devices for Microwave

Switching," IEEE Trans. Electron Devices ED-28, pp. 196-204 (Feb. 1981).

- Ayasli, Y., J.L. Vorhaus, R.A. Pucel, and L.D. Reynolds, "Monolithic GaAs Dis-tributed FET Switch Circuits," IEEE GaAs Integrated Circuit Symposium, Oct. 27, 1981, San Diego, California.

- Ayasli, Y., A. Platzker, J.L. Vorhaus, and L.D. Reynolds, "A Monolithic Single-Chip X-Band Four-Bit Phase Shifter," IEEE MTT-S International Microwave Symposium, Dallas, Texas, June 15-17, 1982.

- Ayasli, Y., R. Mozzi, L. Hanes, and L.D. Reynolds, "An X-Band 10-W Monolithic Transmit-Receive GaAs FET Switch, IEEE Microwave and Millimeter-wave Monolithic Circuits Symposium, Dallas, Texas, June 18, 1982.

- 8. Fukui, H., "Determination of the Basic Device Parameters of a GaAs MESFET," Bell Syst. Tech. J. 58 (3), p. 771 (March

- 9. Berger, H.H., "Contact Resistance on Diffused Resistors,"1969 IEEE ISSCC Digest of Technical Papers, Feb. 1969, pp. 160-161.

- 10. Pucel, R.A., H.A. Haus, and H. Statz, "Signal and Noise Properties of Gallium Arsenide Microwave Field-Effect Transistors," Advances in Electronics and Electron Physics, Vol. 38, p. 195, 1975.

Yalcin Ayasli, received a B.S. degree from Middle East Technical University in Ankara, Turkey, in 1968. His graduate study was at Massachusetts Institute of Technology, where he received an M.S. degree in 1970 and an Sc.D. in 1973, both in electrical engineering. His doctoral thesis research on "Magnetic Semiconductor Interactions" was performed with the microwave and quantum magnetics group at MIT.

From 1973 until 1979 he was a member of the faculty of engineering at Middle East Technical University. His teaching responsibilities included undergraduate and graduate courses on electromagnetic theory, microwave theory, and the electrodynamics of waves, media, and interactions. He also served as assistant chairman to the Electri-

cal Engineering Department.

In September of 1979 Dr. Ayasli joined the semiconductor laboratory of the Raytheon Research Division, where he has been actively engaged in theoretical and experimental studies of microwave monolithic integrated circuit techniques involving field-effect transistors and related devices. He is the author of a number of technical papers.

### **CONTROL LIKE THIS** COMES ONLY FROM ROGERS.

Rogers RT/Duroid® 5870, 5880. The unique microwave laminates with the lowest tolerance in dielectric constant available. Anywhere.

Rogers RT/Duroid with  $\epsilon_r$  + .01 gives you the edge in the most critical microwave circuitry design. It delivers the qualities you look for in a microwave laminate. Closer control. Consistency. Precision. It far exceeds the strict standards of the military, stands up to your toughest demands.

Rogers RT/Duroid offers other advantages, too. A lower dissipation factor than woven cloth structures. And trouble-free processing, with a non-woven glass microfiber construction that prevents wicking.

For closest control. For consistency. For trouble-free processing. And for precision in your most demanding designs, rely on RT/Duroid with €r + .01 You can get this kind of control from precisely one company. Rogers. It's available now. Ask us about it. Call Mike Norris, at (602) 963-4584.

> Rogers Corporation Chandler, Arizona 85224

**POGEPS**

# Yield Considerations in the Design and Fabrication of GaAs MMICs

A.K. Gupta, W.C. Petersen, and D.R. Decker

Rockwell International

Microelectronics Research and Development Center

Thousand Oaks, CA

#### Introduction

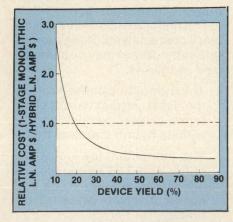

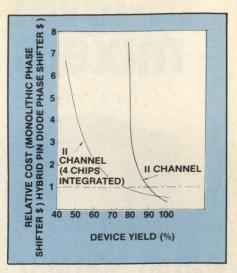

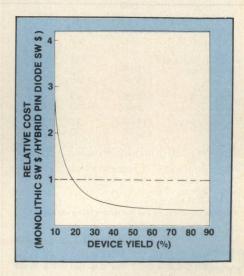

Monolithic Microwave Integrated Circuits (MMICs) fabricated on GaAs substrates are revolutionizing microwave component and systems design.1 The ultimate impact of this new technology on future microwave systems will be determined by the production yields that can be achieved for chips at a given level of performance. Not only will the attainable yields determine system cost/performance tradeoffs, but they will also delimit the extent to which MMIC chips will reach higher levels of system integration with commensurate reduction of size, weight and increased reliability.

At the present stage of development of GaAs MMIC circuitry, the emphasis is on achieving state-ofthe-art performance comparable to or better than that of traditional MIC components. Application areas for MMICs will be highly sensitive to realization of equivalent or superior performance to MIC technology with additional advantages of reduced size, weight, and/or cost. Some applications will be more sensitive to size, weight and reliability considerations and others will be more sensitive to cost factors. MMIC yield will be the most significant factor in determining both chip cost and level of integration, and therefore, achievable yields will be a determining factor in the competitiveness of MMIC technology with established

microwave circuit fabrication techniques.

The complexity of an individual MMIC chip can range from the component level to the subsystem level of circuitry as shown in Table 1. It may be seen from the table that the potential range of functionality of MMICs forms a hierarchy which spans from the individual circuit level to complex electronic subsystems on a chip. Realization of higher functionality MMICs will depend on achieving high overall yields which in turn depend on high component circuit yields.

#### TABLE I MMIC CIRCUIT TYPES

- I. Component Circuits:

Broadband Amplifiers

Low Noise Amplifiers

Mixers (GaAs FET or Schottky

Diode)

Voltage Controlled Oscillators

Power Amplifiers

Binary Phase Shifters

Microwave Switches

- II. Functional Blocks: Integrated Receiver Front End Frequency Synthesizer (PLL) Multi-Bit Phase Shifters MSK Modulator/Demodulator

- III. Multi-Functional Subsystem:

T/R Module for Phased Array Radar

Digital Radio Transmitter/Receiver

Receiver/Signal Processor

Television Receiver and Channel

Selector for DBS

For a given degree of complexity it is possible to partition the circuit-

ry so that MMICs of lower functionality may be interconnected using MIC technology to achieve the desired system performance. The unique advantages of MMIC technology such as small size, light weight, high reliability, and low cost, however, are all enhanced by achieving as high a degree of circuit integration as possible consistent with acceptable overall yields. Therefore, it is seen that the yield issue will be crucial in determining the eventual system impact of GaAs MMIC technology.

Production yields of high performance GaAs MMICs will be determined by the following salient factors:

- GaAs FET and Schottky Diode Yield

- Passive Component Yield

- Distribution of Element Values (Active and Passive)

- Circuit Performance Sensitivity to Element Values

- · Chip Size

The above factors are dependent upon both design approach and fabrication technique. Approaches which are consistent with high production yield of GaAs MMICs are discussed, and representative examples of application of these considerations are described in the ensuing sections.

#### **Design Considerations**

A major design consideration for high yield (and associated lower

cost) is to minimize circuit size. For a constant percentage of good circuits, small size implies more circuits per wafer and therefore higher yield per wafer. However, to obtain a constant "good circuit" percentage on smaller chips, it is necessary to minimize the "critical circuit area" of each chip, i.e., the area sensitive to random failure modes due to contamination, mask defects, etc. Active devices and capacitors are most sensitive to these defects, while inductors, transmission lines, air bridges, and resistors are susceptible to a lesser extent. In addition, process related defects must be minimized by careful process design.

Engineering tradeoffs are necessary in the design of high yield circuits since the requirements for small size and use of a minimum number of "highest risk" elements are often contradictory. For example, broadband active matching consumes much less GaAs real estate then conventional passive reactive tuning elements. However, extra FETs are used which could adversely effect yield although RF performance may be enhanced by the use of active devices. Many similar cases exist, where either active or passive versions of a circuit could be designed. Usually the passive circuit is substantially larger but has higher yield. Examples include power dividers, phase shift networks, directional couplers, and many other components traditionally fabricated as passive circuits. The optimum compromise selected depends on actual processing yield for each of the various components, and no universal compromise exists. Continuous monitoring of yields is needed to make intelligent tradeoffs as the processing technology matures. However, as yields improve, the compromise tends to favor small chips and more active devices. An important additional advantage of this approach, and an indication that GaAs MMIC technology is maturing, is that chips of subsystem complexity can be seriously considered while maintaining reasonable chip size.

In addition to these general design guidelines, many specific

circuit design and layout considerations can significantly increase yield. Some of these, such as capacitor and FET design rules, are dependent on the selected process and will be described later in this paper. Others are strictly circuit considerations which will improve the yield independent of processing techniques. Designs which minimize sensitivity to process variations will produce the highest RF yield. Feedback design is one of the most successful of these techniques at lower frequencies where the associated gain penalties are acceptable. At higher frequencies computer aided design techniques can be utilized to minimize circuit sensitivity to those elements most likely to vary, such as FET gate-to-source capacitance.

As in lower frequency silicon integrated circuits, resistance and capacitance ratios are more accurately controlled than the absolute magnitudes of these components. Designs based on ratios of similar element types will result in higher circuit yields. FET saturation current (Ipss) will also be inversely proportional to resistor values provided the FET active layer is formed by the same ion implant used for resistor fabrication. This advantage, most useful in bias circuit design, is partially lost when high performance FETs with recessed gates are required in the circuit. The use of FETs as active loads or other bias control devices will retain bias tracking but could adversely affect noise and power performance in some designs.

Transmission line impedance variations also track across the chip (via a non-linear relationship) since they are formed with a common GaAs substrate thickness and metalization process. Although not often used in the design process this coupling simplifies sensitivity analysis, since only one common parameter (substrate thickness for microstrip lines) needs to be examined.

#### **Fabrication Techniques**

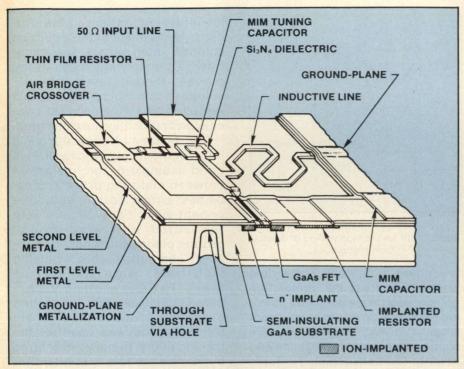

An ion implantation based process has been developed for the fabrication of Gallium Arsenide MMICs incorporating active devices, RF circuitry and all bypass

capacitors. Multiple, localized ion implantation is used for forming optimized active layers and n' contacts for low noise and power FETs, mixer diodes, etc. Contact photolithography is used for all pattern steps. Plasma enhanced CVD silicon nitride is used as the dielectric in metal-insulator-metal (MIM) capacitors and as the insulator in a two level metalization process. Excellent uniformity and reproducibility of MIM capacitors, has allowed their use for both RF tuning and bypassing. Except for resistors, all microwave circuitry, air bridges, and beam leads are on the second metalization level which is electroplated to a thickness of 2-3  $\mu$ m to minimize losses. Backside via holes are etched where necessary. An overview of the fabrication process is presented here and yield limiting factors which have been investigated are discussed.

Figure 1 is a schematic drawing of the various active and passive components comprising an MMIC. These include low noise and power MESFETs, Schottky barrier diodes. thin film and bulk resistors, MIM capacitors for RF tuning and bypassing, transmission lines, air bridges, and backside via holes. Fabrication of an MMIC begins with the synthesis of doping profiles for FET active layers, n+ contacts and bulk resistors by localized Si<sup>+</sup> ion implantation in qualified semi-insulation GaAs substrates. Substrate qualification consists of sampling the front and the tail of the ingot under consideration and checking the doping profile for a standard implant-capanneal cycle. Activation, pinchoff voltage uniformity, and electron mobility are measured and compared with design specifications to determine the suitability of the ingot for MMIC fabrication. The isolation provided by unimplanted regions of the S.I. substrate after undergoing an annealing cycle is also checked. A sheet resistance  $\geq 10^7 \,\Omega$ / is required for passing this test. Data obtained on test wafers from different lots show that I<sub>DSS</sub> uniformity over a ~ 10 cm' wafer before gate recess is typically better than 5% (2  $\sigma$ ) and, for constant implantation dose.

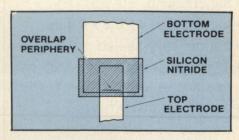

Fig. 1 Schematic drawing of typical MMIC.

reproducibility from run to run is approximately  $10\% (2\sigma)$ . These data were obtained using both Bridgman and LEC (undoped and Cr doped) substrates. I<sub>DDS</sub> reproducibility can be improved by a slight dose adjustment for each ingot as determined by the qualification data.<sup>2</sup>

Following active layer formation, ohmic contacts are formed by sequential evaporation of Au-Ge and Ni, liftoff, and alloying at  $450^{\circ}$ C. This contact formation technique results in reproducible low resistance contacts. Typically,  $r_c \simeq 1 \times 10^{-6} \, \Omega \, \text{cm}^2$ , and this value is maintained through the entire MMIC fabrication process which includes two  $250^{\circ}$ C silicon nitride deposition steps.

After contact metalization, the submicron gates are defined by contact photolithography and liftoff. Gate yield can be a significant circuit yield limiting factor. In addition to broken gates, other defects such as those induced by excessive wafer handling, poor source-drain metal definition, and short circuits caused by metalization defects associated with contact lithography are presently limiting gate dc yield. Short circuits caused by misalignment (due to mask runout, wafer warpage, maskwafer bowing, aligner limitations,

etc.) become important when gate source gaps are reduced to improve device performance. In order to maximize gate yield several precautions are taken. These include monitoring wafer flatness and ensuring that it is in the range of  $\pm$  1  $\mu$ m/inch after capping and annealing, and using 0.090 inch thick masks for minimum distortion during contact printing. Typical dc yield of a 500  $\mu$ m wide FET with a 4.8  $\mu$ m source-drain gap is 92%.

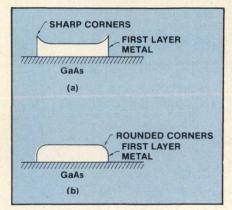

Ti/Au first level metalization provides overlays for ohmic contacts and the lower electrodes of MIM capacitors. This pattern is formed by dielectric aided liftoff to achieve the rounded edges necessary for good capacitor yields. Ion milling and some other liftoff techniques<sup>3</sup> have also been used successfully for this metalization step. A 6000 A layer of silicon nitride is deposited over the first level metal using plasma enhanced chemical vapor deposition (PSN). This forms the dielectric for MIM capacitors and the insulator for second level metal crossovers. Finally, the second metal layer is defined by photolithography and gold electroplating to a thickness of 2-3 µm. The second level metal provides the top electrode of MIM capacitors, plus interconnects, air

bridges and other microwave circuitry.

The uniformity, reproducibility, and dc yield of MIM capacitors has been studied. Data on the first two aspects indicate good control of the thickness and dielectric constant of PSN. A run to run variation of < 8% (2  $\sigma$ ) has been achieved over a period of  $\sim$  2 years. Variation over a wafer is considerably less. Such control has made possible the use of MIM capacitors for RF tuning as well as bypassing applications.

DC yield of MIM capacitors depends on both the area and the length of overlap periphery (Figure 2) between the first and the second metalization levels. It has been possible<sup>2</sup> to obtain a good fit of measured dc yield data to an equation of the form:

$$Y = 1 - \alpha A - \beta P$$

where.

Y = DC yield of MIM capacitor

A = Capacitor area

P = Overlap periphery between first and second metalization levels using linear regression techniques. The area dependence of capacitor yield is due to pinholes in the nitride. In practice, pinholes

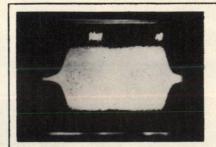

Fig. 2 Typical MIM capacitor with overlap periphery defined.

are associated with debris on the wafer, metal splattering during first level metalization etc., and can be reduced by controlling these factors. The periphery dependence arises due to sharp edges (obtained by direct liftoff, Figure 3a) which are not well covered by PSN and usually result in a short. Rounded edges, as obtained by ion milling or special liftoff techniques<sup>3</sup> (Figure 3b), are more reliably covered by PSN and cause fewer shorts.

Preliminary data on dc probe plus visual (microscopic) circuit yield of three different circuits is

[Continued on page 80]

## 11.5dB directional couplers

# **0.5** to 500 MHz only \$1195 (5-49)

IN STOCK...IMMEDIATE DELIVERY

- MIL-C-15370/18-002 performance\*

- low insertion loss, 0.85dB

- high directivity, 25dB

- flat coupling, ±0.5dB

- miniature, 0.4 x 0.8 x 0.4 in.

- hermetically-sealed

- 1 year guarantee

\*Units are not QPL listed

#### PDC 10-1 SPECIFICATIONS

FREQUENCY (MHz) 0.5-500 COUPLING, dB 11.5

| INSERTION LOSS, dB   | TYP.   | MAX. |

|----------------------|--------|------|

| one octave band edge | 0.65   | 1.0  |

| total range          | 0.85   | 1.3  |

| DIRECTIVITY, dB      | TYP.   | MIN. |

| low range            | 32     | 25   |

| mid range            | 32     | 25   |

| upper range          | 22     | 15   |

| IMPEDANCE            | 50 ohr | ns.  |

For complete specifications and performance curves refer to the Microwaves Product Data Director, the Goldbook, EEM, or Mini-Circuits catalog

For Mini Circuits sales and distributors listing see page 85

finding new ways . . . setting higher standards

### Mini-Circuits

A Division of Scientific Components Corporation World's largest manufacturer of Double Balanced Mixers 2625 E. 14th St. B'klyn, N.Y. 11235 (212) 769-0200

C 79-3 REV. B

Fig. 3 First layer metal definition by (a) direct liftoff and (b) ion milling or special liftoff techniques.

presented in Table 2. These data were obtained at the completion of front end processing and do not include attrition due to subsequent steps involving thinning, via hole etching, backside metalization and sawing. The data depicted in Table 2 are commensurate with individual component yields and indi-

limitations elsewhere in the process. Nevertheless, the optimum solution often entails simultaneously altering many steps in the process. Therefore seemingly poor solutions to a yield problem must be followed to their logical conclusion before they are eliminated.

The history of capacitor yield improvements at Rockwell is a good example of the interaction between maturing process capabilities, circuit design, and component yield. Early circuits were fabricated with wrap-around ground planes since no thru-substrate via holes were available (substrates were still 10 mils thick). To avoid shorting the bypass capacitors while connecting the sheet ground to the chip, the top electrode was used as the ground plane. Initial yield of large bypass capacitors was often below 10%, and they were quickly identified as the "weakest-link."

| TABLE II  DC CIRCUIT YIELD |                     |                     |                    |

|----------------------------|---------------------|---------------------|--------------------|

|                            | Buffer<br>Amplifier | Driver<br>Amplifier | Power<br>Amplifier |

| Total Gate                 |                     |                     |                    |

| Periphery (mm)             | 0.2                 | 1.0                 | 1.98               |

| Source-Drain<br>Gap (μm)   | 3.8                 | 4.8                 | 4.8                |

| Total MIM Capacitance (pF) | 20                  | 49.4                | 50.8               |

| FET Yield (%)              | 81                  | 86                  | 59                 |

| Capacitor<br>Yield (%)     | 97                  | 88                  | 76                 |

| Circuit Yield (%)          | 78                  | 76                  | 47                 |

cate the potential for achieving high overall yields of functional MMIC modules with subsystem complexity.

Data on component yield are obtained in the process of correcting known yield problems. The "weakest link" technique, i.e., detecting the most serious problem, developing process and/or circuit changes to increase yield, and then determining the new yield limiting factors, is a powerful method of increasing circuit yield. Proper application requires sufficient processing volume to obtain meaningful yield data, and detailed consideration of the entire processing sequence after every proposed change in fabrication. It is common to solve one yield problem by inserting more severe

As described previously, the major yield problems were pinholes in the dielectric (silicon nitride) and "spikes" on the edges of the bottom layer metal. Steps were taken to round the metal edges and reduce contaminiation, resulting in significant yield improvements. As the process matured via holes were added and wraparound grounds could be eliminated. Placing the ground on the bottom layer allowed the edge (with potential spikes) to be outside the top metal around most of the capacitor periphery. Yield was once again improved at the same time RF performance was improved by lower grounds. Finally, the addition of the high yield air bridges (needed for low capacitance crossovers) allowed the to-

[Continued on page 82]

#### [From page 80] DESIGN AND FABRICATION

tal elimination of overlap induced shorts. Yield of large bypass capacitors is now over 90% and they no longer represent the weakest processing link.

Based on these and other similar yield considerations, many circuits have been successfully designed and fabricated. Three representative examples will be summarized here. The first<sup>4</sup> is a broadband amplifier initially designed over two years ago for the Army which still dramatically demonstrates the power of active matching techniques. High FET yield allows the use of two extra active devices to reduce chip size and improve performance without

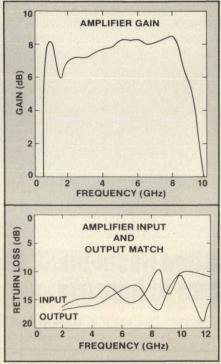

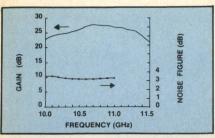

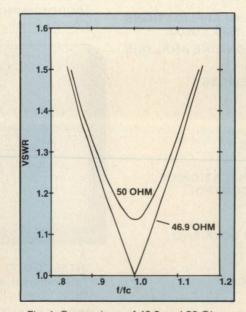

Fig. 4 Measured gain (a) and VSWR (b) of the broadband MMIC amplifier.

significant yield penalties. Figures 4a and 4b show the measured gain and VSWR performance respectively. Initial yield was poor due to capacitor shorts (the chip has over 130 pF total capacitance) but was later improved. This device prompted much of the capacitor yield studies which lead to the present capacitor design.

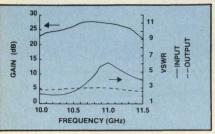

The second circuit example is a two stage 8 GHz amplifier developed for the Navy<sup>5</sup> which demonstrates the need for extensive computer modeling. Accurate element and parasitic models allowed layout on a two millimeter square chip with all passive matching circuits. On chip resistive bias networks and bypass capacitors reduced external connections to just two RF and two dc lines (plus a

Fig. 5 Measured gain of a two stage monolithic amplifier.

sheet ground). Figure 5 shows the measured gain of this amplifier chip.

The final example<sup>6</sup> demonstrates the advantage of feedback which reduces sensitivity to process variations. At low frequencies resistive negative feedback provides broadband input and output match with flat gain and toler-

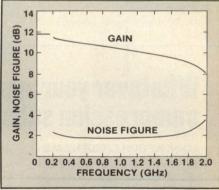

Fig. 6 Measured gain and noise figure of an amplifier with resistive feedback.

ance to variations in the active and passive device parameters. Figure 6 shows the measured gain and noise performance of this type of amplifier. Since a large device is needed to obtain sufficient transconductance to operate in the resistive feedback mode, output power in excess of 20 dBm is obtained as a byproduct of this design method.

All three amplifiers described above can be fabricated with high dc yield. RF yield will vary between them, with the feedback amplifier least sensitive to process variations and the broadband

amplifier most sensitive. It should be noted that active matching and feedback techniques are particularly insensitive to process variations, and both will be more widely used in the future.

#### Conclusions

The above descriptions of design approaches and fabrication techniques to achieve high yield of GaAS MMICs set the stage for consideration of the impact of yield on chip cost and multicircuit capability. To first order, the yield of higher complexity MMICs can be approximated as the product of the yields of the constituent circuits. Referring to the hierarchy of MMIC circuit types described earlier, it is seen that chip complexity in terms of the number of component circuits on chip naturally falls into one of the following ranges:

### MMIC FUNCTIONALITY AND CHIP COMPLEXITY

FUNCTIONALITY CHIP COMPLEXITY

(# OF CIRCUITS)

Single Component Functional Block Multi-functional

Subsystems

1 to 3 4 to 10

11 or more

where, in the above classification scheme, each gain stage of an amplifier is counted as a separate circuit for the purpose of determining complexity.

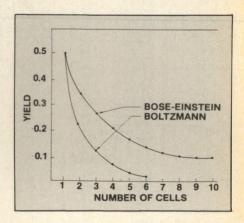

From the preceding sections it may be seen that the yield for a

single (medium power) amplifier stage may range between 50 and 80% including dc testing and microscopic visual inspection. Microwave testing may be expected to incur an additional yield factor which may range from 50 to 90% depending on design sensitivity and process control. In the simplest analysis, then, the yield of a single component MMIC could be as high as 37 to 72%, assuming the best dc yields observed, and an RF yield of 90%. On the other hand, the best yields for functional block MMICs based on the same assumptions are in the range of 3.7% to 27% and the best yields for multifunctional subsystem MMICs are in the range of 0 to 2.7%. Obviously the present analysis is over simplified since the multi circuit yields quoted above are estimated by taking the nth power of the estimated individual circuit yield. However, just from doing the above exercise it becomes obvious that multicircuit MMIC yields may be quite low even with respectable single stage vields.

The point of all this talk about yields is to suggest that in the hierarchy of MMIC functionality described above, a point is reached at which it no longer makes sense to put additional circuits on a single chip, and that, for reasons of cost and overall yield, the circuitry should be partioned and interconnected using MMIC tech-

nology to realize the total functionality. The level of complexity at which the partitioning should occur is dependent on both the attainable yields at a given stage of development of the technology and on the cost sensitivity of the application as well as competition for the same application from existing technology. At the present time, it appears feasible to develop and use MMIC technology at the component level (up to several stages) and to a certain extent at the functional block level albeit with somewhat lower yields. As the GaAs MMIC technology matures, it is anticipated that multifuntional subsystem chips will become technically and economically feasible, and that functional block type chips will become highly competitive with other microwave circuit approaches for applications with a substantial volume requirement.

#### REFERENCES

Podell, A.F., "GaAs MMICs: Expensive, Exotic, but Exciting, "Microwaves, pp. 54-61, December 1980.

Gupta, A.K., W.C. Petersen, and D.R. Decker, "Yield Considerations for Ion Implanted GaAs MMIC's," to be published in the January 1983 issue of the IEEE Transactions on MTT.

Hatzakis, M., B.J. Canavello, and J.M. Shaw, "Single Step Optical Lift-Off Process," IBM J. Res. Develop. 24, No. 4, pp. 452-460, July 1980.

4. Petersen, W.C., D.R. Decker, A.K. Gupta, J. Dully, and D.R. Ch'en. "A Monolithic GaAs O.1 to 10 GHz Amplifier," 1981 IEEE MTT-S International Microwave Symposium Digest, pp. 354-355. [Continued on page 84]

#### [From page 83] DESIGN AND FABRICATION

- Gupta, A., D.R. Decker, W.C., Petersen, "Monolithic Gallium Arsenide Super-heterodyne Front End," Final Report for ONR Contract No. N00014-78-C-0624

- Petersen, W.C., A.K. Gupta, D.R. Decker, "A Monolithic GaAs dc to 2 GHz Feedback Amplifier," to be published in the January 1983 issue of the IEEE Transactions on MTT.

W. C. Petersen, member of Technical Staff, Microwave Devices Section, received his B.S. degree in Electrical Engineering in 1971 from New York University and his M.S. and Ph.D. degree in Electrical Engineering in 1973 and 1976, respectively from Cornell University. In 1976 he joined Varian Associates where he was engaged in the design and development of various microwave FET and bipolar amplifier, including low noise, high power, and broadband limiting amplifiers. He is an author of several computer aided design programs used for both network analysis and synthesis. In 1979 he joined Rockwell International where he is presently engaged in

the research and development of monolithic GaAs microwave integrated circuits. He is a member of Tau Beta Pi, Eta Kappa Nu. and the IEEE.

Aditya Gupta, member of Technical Staff, Microwave Devices Group, received his B. Tech. degree in 1973 from the Indian Institute of Technology, Kanpur, India, and his M.S. and Ph.D. degrees from Cornell University in 1975 and 1978 respectively. While at Cornell, he worked on the power combining of high power, x-band, IMPATT oscillators and on the design and fabrication of ion implanted silicon n<sup>+</sup>pπp<sup>+</sup> Read IMPATT Diodes. Dr. Gupta join the Science Center in 1978 and is presently engaged in the design, fabrication and characterization on monolithic microwave integrated circuits.

D. R. Decker, manager, Microwave Devices, received his B.S., Physics from North Carolina State University; M.S., Physics and Ph.D., Electrical Engineering from Lehigh University. Since joining the Rockwell International Microelectonics Re-

search and Development Center in 1978, Dr. Decker had been active in the research and development of GaAs microwave devices. His current interests are in the design and development of GaAs monolithic microwave integrated circuits for broadband amplifiers, power amplifiers, balanced mixers, digital phase shifters, feedback amplifiers and integrated receiver front end applications, development of very low noise GaAs FETs, and modeling and design techniques for large-signal microwave ciruitry.

Prior to joining Rockwell, Dr. Decker has had extensive experience in microwave device and circuit technology. In 1976, he joined the National Radio Astronomy Observatory in Charlottesville, Virginia, where he was engaged in research and design of low noise millimeter wave receivers. In 1975, he joined Hewlett Packard Co. in Palo Alto, California, where he worked on low noise and high power GaAs FETs and circuits. Dr. Decker has two patents in GaAs FET Technology, and is a senior member of the IEEE.

# DIGITAL ATTENUATORS

- Attenuation Range to 127 dB

- Frequency Range DC to 400 MHz

- TTL Programmable

- Bits: One to Eight

- Switch Times as low as 200 Nanoseconds

- Intercept Point to +45 dBm (3rd order)

- Transient Suppression as low as 10 mV

- Construction—Solid State or **Electro-mechanical**

Lorch Electronics announces a new line of TTL Compatible Digital Attenuators. Series DA-600, DA-700 and DA-800 are miniature components capable of providing digital attenuation with a precision normally associated with traditional mechanical step-attenuators.

Write, phone or circle reader service number for literature.

ORCH ELECTRONICS CORP.

105 CEDAR LANE, ENGLEWOOD, NEW JERSEY 07631 • 201-569-8282 • TWX: 710-991-9718

## Broadband Monolithic Integrated Power Amplifiers in Gallium Arsenide

M. C. Driver, G. W. Eldridge, and J. E. Degenford Westinghouse R&D Center Pittsburgh, PA

#### Introduction

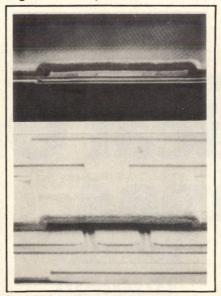

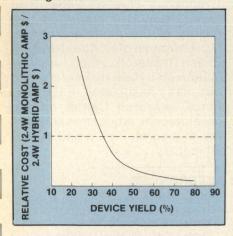

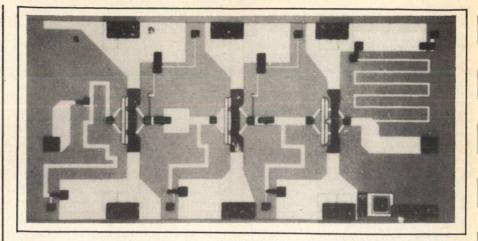

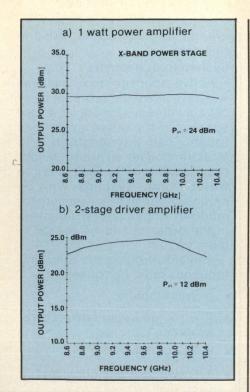

The use of monolithic microwave integrated circuits is necessary to maximize performance and reduce cost of power amplifiers (1-10 watts) at S- to X-band frequencies and above. Performance is enhanced because the close spacing of field effect transistors (FET's) used in the multistage amplifiers allows almost identical device characteristics and, in addition, the tuning elements in microstrip and lumped element forms can be fabricated close to the active elements, thereby reducing losses. Cost is reduced because silicon-like processing can be used on wafers ground to 2 in. diameter with orientation flats resulting in DC yields of up to approximately 40% for 2-stage, 1 watt amplifiers (50 amplifiers/ wafer). Low costs are necessary for phased array applications where many thousands of identical amplifiers are employed. The hybrid realization of similar amplifiers is considerably more expensive.

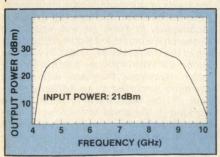

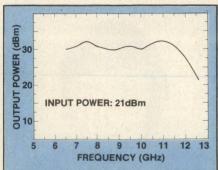

This paper describes the development of two designs of 2-stage monolithic integrated amplifiers in gallium arsenide covering the 5 to 10 GHz and 8 to 12 GHz bands. The amplifiers were fabricated using ion implantation of Si<sup>29</sup> directly and selectively into undoped, semi-insulating gallium arsenide grown by the Czochralski technique in-house at Westinghouse.

The passive elements in the

amplifiers are a combination of microstrip and lumped elements to produce low-loss impedance-transformers, power splitters and power combiners. Both interdigital and overlay Metal-Insulator-Metal (MIM) capacitors have been used in the circuits. The MIM capacitor is favored because of its smaller size and higher Q. Together with the submicron gates of high frequency amplifiers, the MIM capacitor is the lowest yield element in these monolithic cir-

cuits (~95%). Both via construction (connections between the ground plane on the back of the wafer and grounded elements on the front of the wafer) and air bridge fabrication have yields that are better than 99%.

#### **RF Design Methods**

The cost and performance advantages of minimizing chip size preclude the commonly used balanced amplifier approach to wideband performance since it requires

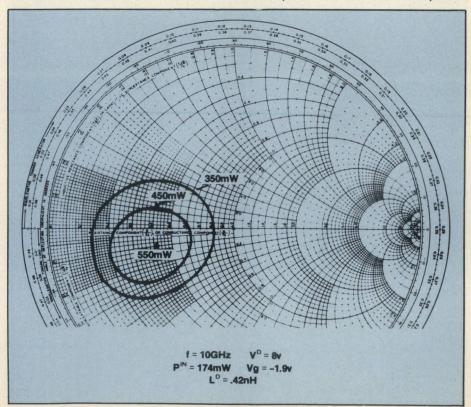

Fig. 1 Load pull circles for 1200µ FET.

relatively large quadrature couplers on the input and output of each stage in addition to matched amplifier pairs. At Westinghouse a single ended approach was taken, which is based on load-pull characterization of the FET's and has been used to design a number of 2-stage, 5 to 10 GHz and 8 to 12 GHz monolithic amplifiers with power outputs of 1 watt. The approach may be summarized as follows:

- For a given fixed input power level, load-pull contours are plotted corresponding to constant power output at each frequency.

- The output circuit (or interstage circuit in the case of the first stage) is designed to present an impedance locus which crosses these constant power contours in a manner to provide constant power at each frequency.

Thus, the output circuit provides the optimum load impedance at the highest frequency of interest while selectively "de-optimizing" the load impedance at lower frequencies to provide constant power (and gain).

The "load-pull" measurements give data on how the output power of each FET varies as a function of the load impedance presented to it. The load impedance is varied electronically to any value and the corresponding output power measured, resulting in a series of constant power contours for a fixed input power and bias point generated at each frequency of interest in the design band. Such a set of contours is shown in Figure 1 for a 1200 µm first stage FET at an input power of 174 mW at 10 GHz. The bias point for this FET is  $V_{DS} = 8V$ ,  $V_{GS} = -1.9V$ , and  $I_{D} = 150$ mA. At each frequency there is only one load impedance, which when presented to the FET, results in maximum output power for a given input power. At 10 GHz, the 1200 um FET has a maximum power output of 550 mW. This power level is particularly important since, according to our design approach to gain equalization, the maximum output power at the highest frequency in the design band governs the output power of that stage across the band.

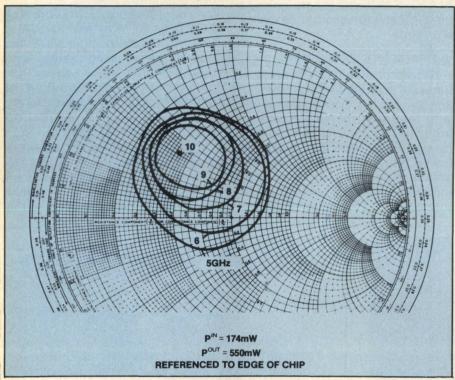

At 7 GHz (Figure 2), the maximum output power has risen to 695 mW. The 550 mW level, which

1 = 7GHz V<sup>O</sup> = 8v P<sup>IN</sup> = 174mW Vg = -1.9v L<sup>D</sup> = .42nH

Fig. 2 Load pull circles 1200µ FET.

was attainable by only one load impedance at 10 GHz, is now attainable by impedances lying on the locus shown at 7 GHz since the FET must be power mismatched to produce less than maximum output power. The loci of impedances at 5 GHz producing the 550 mW level is even larger since the mismatch must be even greater.

If the 550 mW load-pull circles at each frequency are all plotted on one Smith chart, the composite contours shown in Figure 3 result. Note that the composite contours are shifted more to the inductive end of the Smith chart than the individual frequency contours. This is due to the fact that the bondwires used to connect the FET to the test fixture have been accounted for since they obviously are not present in the monolithic amplifier. The composite contours represent not only constant output power, but also constant gain.

With these composite load-pull contours determined, the design problem becomes one of designing the output circuit (or interstage circuit in the case of the first stage) to present an impedance locus which crosses the constant power contours in a manner to provide constant power at each frequency. Such a procedure is complicated and has been described in detail in an earlier article.<sup>2</sup>

Once the initial lumped element circuit parameters and basic circuit topology have been determined, the circuit is converted to a distributed model. To do this, the lumped inductors are replaced by short pieces of microstip transmission line. Shunt parasitic capacitances associated with interdigital capacitors over a ground plane are also added and the entire network is optimized using a special computer algorithm to optimize the impedance locus fit to the composite load-pull contours.

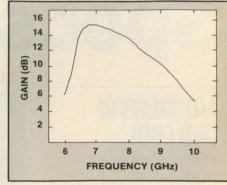

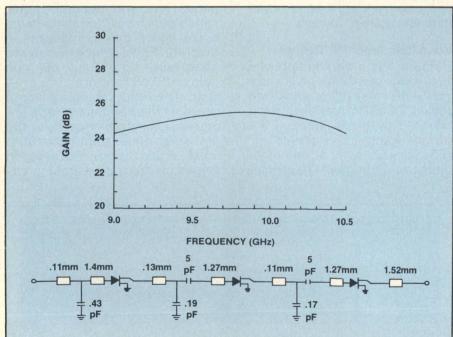

This design procedure has been used to realize a 5 - 10 GHz monolithic amplifier and an 8 - 12 GHz monolithic amplifier incorporating a 1200  $\mu$ m periphery power FET and a 2400  $\mu$ m periphery power

FET. The design goals were 1 watt of output power and 10 dB gain for the 5 - 10 GHz chip and 0.6W output power for the 8 - 12 GHz chip.

#### **IC Fabrication Techniques**

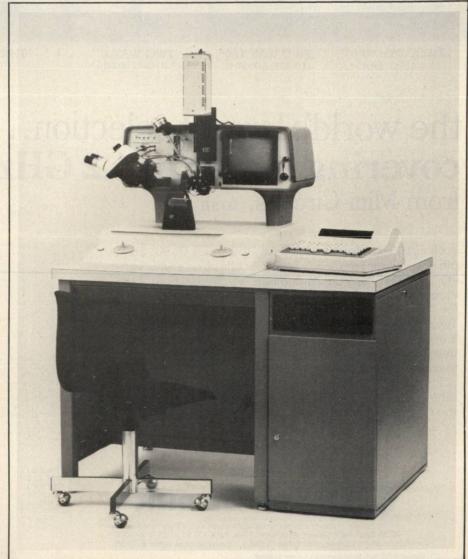

#### — Material Growth

The gallium arsenide semiinsulating substrates used for the fabrication of monolithic integrated circuits are produced inhouse from <100>-oriented, single crystals grown by the liquid encapsulated Czochralski (LEC) technique using a Melbourn highduring processing. As grown, the material exhibits sheet resistivities (R<sub>s</sub>) of 3×10<sup>8</sup> Ω/square and mobilities of 5000 cm<sup>2</sup>/volt-sec. This mobility can be attributed to ~ 1×10<sup>16</sup>/cm<sup>3</sup> residual shallow acceptors (carbon) and an equivalent density of ionized deep donors (EL2).3 The concentration of the residual shallow acceptors varies from 1×10<sup>16</sup>/cm<sup>3</sup> at the seed end of the crystal to 2×1016/cm3 at the tang end and this variation (1×10<sup>16</sup>/cm<sup>3</sup>) represents the change in activation of the Si29 implant that can be expected along

Fig. 3 Composite load pull circles 1200µ FET.

pressure puller (Metals Res. Ltd.). The crystals are pulled from the melt contained in a pyrolytic boron nitride (PBN) crucible following compounding in-situ; a liquid B<sub>2</sub>O<sub>3</sub> encapsulant and inert gas overpressure are employed to prevent As sublimation which would result in low resistance, nonstoichiometric crystals.

Careful elimination of electrically active impurities, particularly Si which can be introduced by SiO<sub>2</sub> crucibles, eliminates the need to counter-dope with Cr to compensate residual shallow donors. These crystals exhibit state-ofthe-art chemical purity and minimize residual impurity activation

the crystal.

The implantation process in use preserves  $R_s \ge 2 \times 10^7 \Omega/\text{square}$ and  $\mu_{\rm H} > 4000$  cm<sup>2</sup>/volt-sec in unimplanted areas. The crystals are ground to 2" diameter and flatted along <100> directions prior to on axis slicing. Lapping and polishing yields approximately 100, 0.020" thick wafers.

#### - Ion Implantation

Implantation processing originates with plasma deposition of a 900 Å Si<sub>3</sub>N<sub>4</sub> primary encapsulation layer on the front surface. This layer remains on the surface through processing to prevent mechanical damage and/or chemical contamination as well as to

[Continued on page 90]

# distortion

hi level (+17 dBm LO)

## 5 to 1000 MHz only \$3195 (5-24)

IN STOCK ... IMMEDIATE DELIVERY

- · micro-miniature, pc area only 0.5 x 0.23 inches

- RF input up to + 14dBm

- quaranteed 2 tone, 3rd order intermod 55 dB down at each RF tone 0dBm

- flat-pack or plug-in mounting

- low conversion loss, 6.2dB

- hi isolation, 40 dB

- MIL-M-28837/1A performance\*

- one year guarantee

\*Units are not QPL listed

#### TFM-2H SPECIFICATIONS

| FREQUENCY RANGE, (MHz) LO, RF 5-1000 IF DC-1000 |      |      |

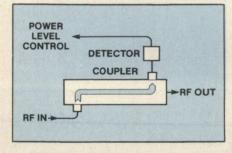

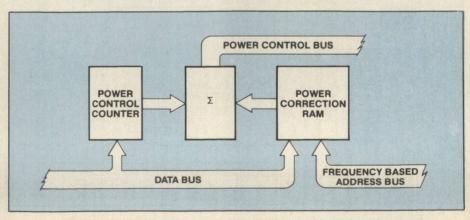

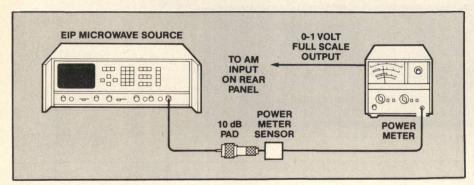

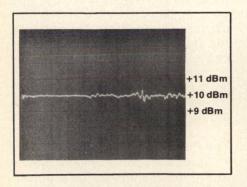

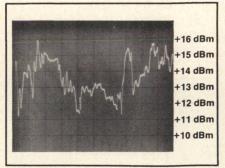

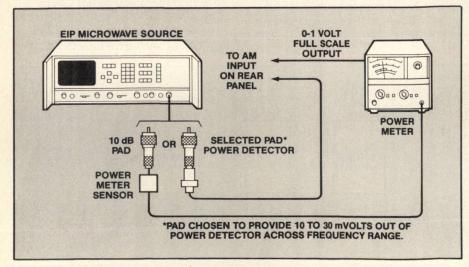

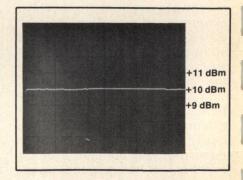

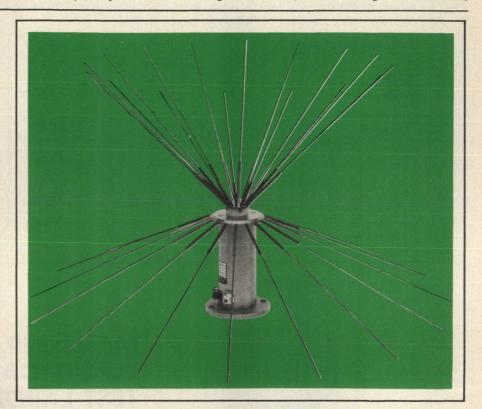

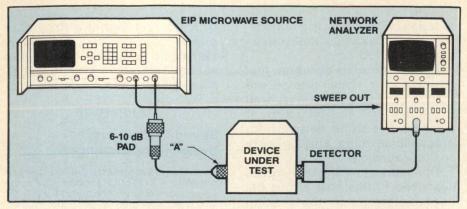

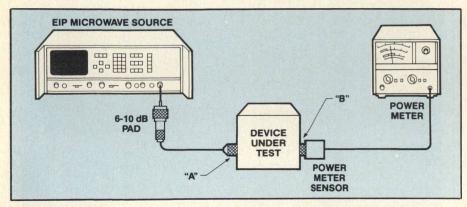

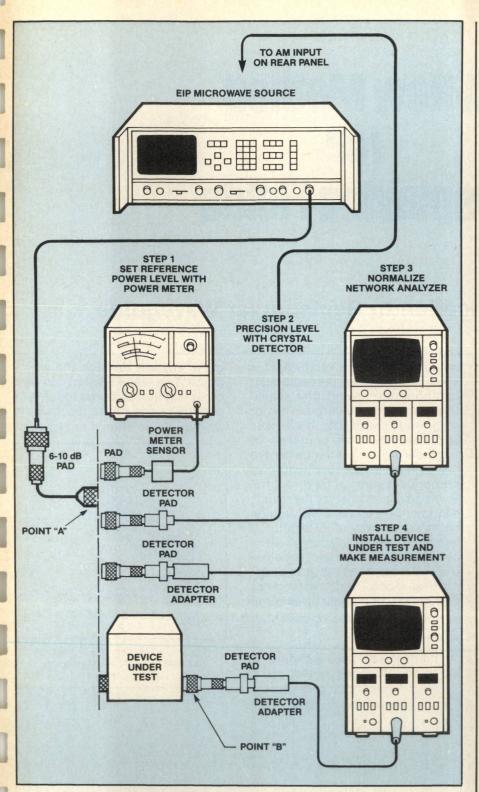

|-------------------------------------------------|------|------|